### Low-Noise Local Oscillator Design Techniques using a DLL-based Frequency Multiplier for Wireless Applications

by

## **George Chien**

B.S. (University of California, Los Angeles) 1993M.S. (University of California, Berkeley) 1996

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Sciences

in the

### GRADUATE DIVISION

of the

## UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Paul R. Gray, Chair Professor Robert G. Meyer Professor Paul K. Wright

Spring 2000

The dissertation of George Chien is approved:

Professor Paul R. Gray, Chair

Professor Robert G. Meyer

Professor Paul K. Wright

University of California, Berkeley

Fall 1999

Date

Date

Date

Low-Noise Local Oscillator Design Techniques using a DLL-based Frequency Multiplier for Wireless Applications

Copyright © 2000

by

George Chien

#### Abstract

## Low-Noise Local Oscillator Design Techniques using a DLL-based Frequency Multiplier for Wireless Applications

by

**George Chien**

### Doctor of Philosophy in Engineering -Electrical Engineering and Computer Sciences

#### University of California, Berkeley

### **Professor Paul R. Gray, Chair**

The fast growing demand of wireless communications for voice and data has driven recent efforts to dramatically increase the levels of integration in RF transceivers. One approach to this challenge is to implement all the RF functions in the low-cost CMOS technology, so that RF and baseband sections can be combined in a single chip. This in turn dictates an integrated CMOS implementation of the local oscillators with the same or even better phase noise performance than its discrete counterpart, generally a difficult task using conventional approaches with the available low-Q integrated inductors. This is a particularly severe problem in RF systems such as AMPS, where the channel spacing is small and close-in phase noise must be extremely low.

In this thesis the fundamental performance limit of a local oscillator design using a DLL-based frequency multiplier is investigated. The distinctive timing jitter accumulation pattern of a DLL-based frequency multiplier is analyzed in detail to predict the phase noise performance based on the thermal-noise-induced jitter of the source-coupled differential CMOS delay cell implementation. The result suggests an unique phase noise signature compared to a PLL approach using a VCO. Due to the limited timing jitter

accumulation in a DLL, the close-in phase noise performance of the DLL-based frequency multiplier is much lower than that of a monolithic VCO.

The specific research contributions of this work include (1) proposing a new local oscillator architecture using a DLL-based frequency multiplier that breaks the traditional LO phase noise limitations, (2) an analytical model that describes the phase noise performance of the proposed local oscillator architecture, (3) the application of the DLL-based frequency multiplier to a monolithic CMOS low-phase-noise local oscillator for cellular telephone applications.

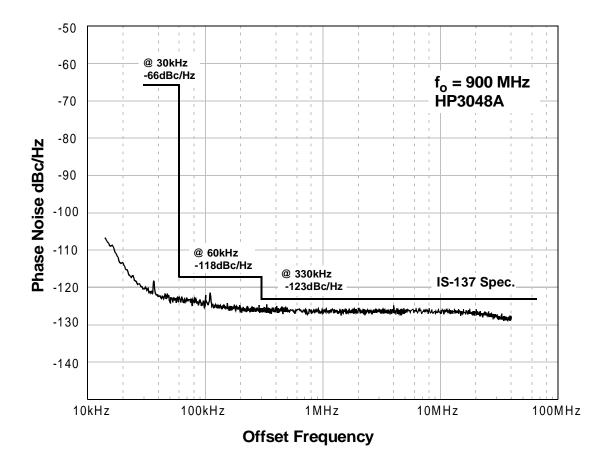

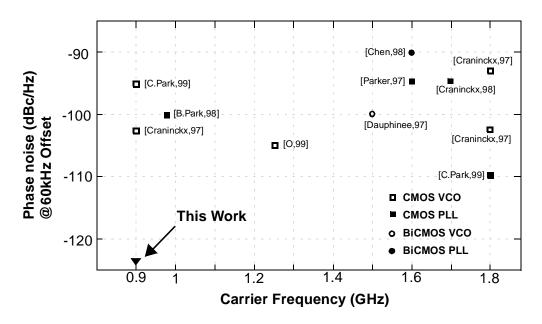

To demonstrate the proposed concept, a fully integrated CMOS local oscillator utilizing a DLL-based frequency multiplier technique to synthesize a 900MHz carrier with low close-in phase noise was designed. This prototype, implemented in a standard 0.35µm CMOS technology, achieves -123dBc/Hz phase noise at 60kHz offset while dissipating 130mW from a 3.3V supply, meeting the requirements of the IS-137 dual-mode standard.

Approved By:

Paul R. Gray, Committee Chair

# **Table of Contents**

# Chapter 1 Introduction

| 1.1 Motivation          | 1 |

|-------------------------|---|

| 1.2 Research Goals      | 4 |

| 1.3 Thesis Organization | 5 |

| 1.4 References          | 6 |

# **Chapter 2** Frequency Synthesizer in Wireless Communication Systems

| 2.1 Introduction                                              | 8  |

|---------------------------------------------------------------|----|

| 2.2 Receiver Architecture                                     | 10 |

| 2.2.1 Superheterodyne                                         | 11 |

| 2.2.2 Direct Conversion (Zero-IF)                             | 13 |

| 2.2.3 Low-IF Architecture                                     | 16 |

| 2.2.4 Block-Down Conversion: Wideband IF with Double          |    |

| Conversion                                                    | 18 |

| 2.3 Transmitter Architecture                                  | 20 |

| 2.3.1 Direct Conversion Transmitter                           | 21 |

| 2.3.2 Double Conversion Transmitter                           | 23 |

| 2.3.3 PLL-based Transmitter                                   | 25 |

| 2.3.4 Summary                                                 | 26 |

| 2.4 Non-idealities in Frequency Synthesizer and Their Impacts | 27 |

| 2.4.1 Role of Frequency Synthesizer                           | 27 |

| 2.4.2 Phase Noise                                             | 30 |

| 2.4.3 Spurious Tones                                          | 36 |

| 2.5 Summary                                                   | 41 |

| 2.6 References                                                | 41 |

# **Chapter 3** Frequency Synthesizer Architectures

| 3.1 Introduction                              | . 44 |

|-----------------------------------------------|------|

| 3.2 Phase Locked Loop Fundamentals            | . 46 |

| 3.2.1 PLL Linearized Model                    | . 47 |

| 3.2.2 Performance Limitation                  | . 51 |

| 3.2.3 Current Approach                        | . 52 |

| 3.3 Integrated Voltage Controlled Oscillators | . 54 |

| 3.3.1 Monolithic Integrated LC-tank           | . 55 |

| 3.3.2 Process-Enhanced Inductors              | . 57 |

| 3.3.3 Integrated Ring Oscillator VCO60                       |

|--------------------------------------------------------------|

| 3.3.4 Micromachined-Based VCO                                |

| <i>3.3.5 Summary</i>                                         |

| 3.4 Architecture Alternatives for Frequency Synthesizers63   |

| 3.4.1 Wide Loop Bandwidth PLL                                |

| 3.4.2 New Architecture for Narrow-Channel Wireless System 65 |

| 3.5 Summary                                                  |

| 3.6 References                                               |

# Chapter 4 DLL-based Frequency Multiplier Fundamentals

| 4.1 Introduction                                         | • | • • |       | 7   | 0' |

|----------------------------------------------------------|---|-----|-------|-----|----|

| 4.2 The Basics                                           |   | • • |       | . 7 | 1  |

| 4.2.1 Operation                                          |   | •   |       | 7   | '2 |

| 4.2.2 Timing Jitter Accumulation                         | • | •   | •••   | 7   | 14 |

| 4.3 Performance Analysis                                 |   | •   |       | 7   | 6  |

| 4.3.1 Phase Noise                                        |   |     |       |     |    |

| 4.3.2 Spurious Tones                                     | • | •   | · • • | 8   | 35 |

| 4.4 Performance Implications for Wireless Communications |   |     | •••   | 8   | 39 |

| 4.4.1 Phase Noise                                        |   | •   |       | . 8 | 39 |

| 4.4.2 Spurious Tones                                     | • | •   | · • • | 9   | )2 |

| 4.5 Summary                                              |   | •   |       | 9   | )4 |

| 4.6 References                                           |   | • • |       | 9   | 95 |

# **Chapter 5** *CMOS Local Oscillator Design using the DLL-based Frequency Multiplier Technique*

| 5.1 Introduction                     | . 97 |

|--------------------------------------|------|

| 5.2 Small-Signal AC Model            | . 98 |

| 5.2.1 Voltage-Controlled Delay Line  | . 99 |

| 5.2.2 Phase Detector and Charge Pump | 102  |

| 5.2.3 Loop Filter                    | 104  |

| 5.2.4 Overall DLL Transfer Function  | 104  |

| 5.2.5 Edge Combiner                  | 107  |

| 5.3 CMOS Delay Stage Design          | 109  |

| 5.3.1 Basic Delay Chain Design       | 110  |

| 5.3.2 Interstage Gain Consideration  | 111  |

| 5.3.3 Voltage Swing Consideration    | 112  |

| 5.3.4 Replica Bias Circuit           | 115  |

| 5.3.5 Implementation                 | 116  |

|                                      |      |

|            | 5.4 Control Circuitry Design       118         5.4.1 Phase Detector       118         5.4.2 Charge Pump       122         5.4.3 Loop Filter       125         5.5 Edge Combiner       128         5.6 Summary       129         5.7 References       130                                                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 6  | Prototype Implementation                                                                                                                                                                                                                                                                                                                                                                         |

|            | 6.1 Introduction       131         6.2 IS-137 Dual-Mode Standard       131         6.3 Technology       135         6.4 Chip Overview       135         6.5 Master Bias       138         6.6 Output Buffer       139         6.7 Performance Estimation       139         6.8 1/f Noise       142         6.9 Layout       142         6.10 Summary       146         6.11 References       147 |

| Chapter 7  | Experimental Results                                                                                                                                                                                                                                                                                                                                                                             |

| -          | 7.1 Introduction       149         7.2 Test Setup       149         7.3 Phase Noise Performance       153         7.4 Spurious Tone Performance       155         7.5 Summary       157         7.6 References       160                                                                                                                                                                         |

| Chapter 8  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                       |

| _          | 8.1 Conclusion                                                                                                                                                                                                                                                                                                                                                                                   |

| Appendix A | RMS Timing Jitter for Differential Delay Cell                                                                                                                                                                                                                                                                                                                                                    |

|            | A.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                 |

|            | A.2 RMS Timing Jitter Analysis                                                                                                                                                                                                                                                                                                                                                                   |

| A.3 Implications | <br>168 |

|------------------|---------|

| A.4 References   | <br>169 |

# **Appendix B** Autocorrelation and Power Spectra

| B.1 Introduction | 70 |

|------------------|----|

| B.2 Theory       | 70 |

| B.3 Example      | 72 |

| B.4 Reference    | 75 |

# **List of Figures**

| Fig. 2.1:  | Conceptual Block Diagram for Wireless Transceiver                   |

|------------|---------------------------------------------------------------------|

| Fig. 2.2:  | Superheterodyne Receiver Block Diagram                              |

| Fig. 2.3:  | Direct Conversion Receiver Block Diagram                            |

| Fig. 2.4:  | Low-IF Receiver Block Diagram                                       |

| Fig. 2.5:  | Wideband IF with Double Conversion Receiver Block Diagram 19        |

| Fig. 2.6:  | Functional Block Diagram for Wireless Transmitter                   |

| Fig. 2.7:  | Direct Conversion Transmitter Block Diagram                         |

| Fig. 2.8:  | Direct Conversion Transmitter with Offset LO                        |

| Fig. 2.9:  | Double Conversion Transmitter                                       |

| Fig. 2.10: | Integrated Double Quadrature Transmitter Architecture               |

| Fig. 2.11: | PLL-based Transmitter Architecture                                  |

| Fig. 2.12: | RF Section of Superheterodyne Receiver                              |

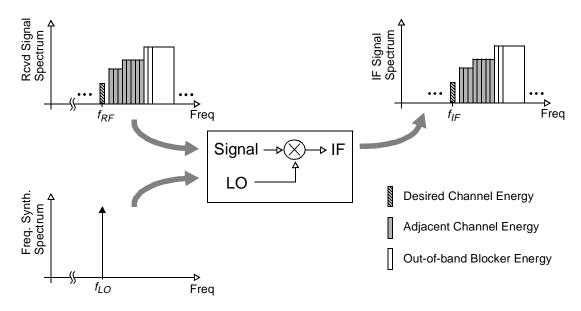

| Fig. 2.13: | Frequency Translation with Ideal Frequency Synthesizer Spectrum. 29 |

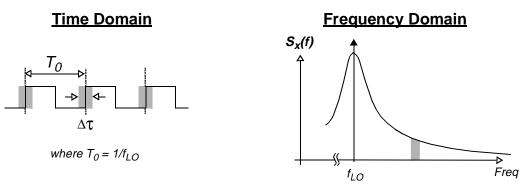

| Fig. 2.14: | Time and Frequency Representations of Phase Noise                   |

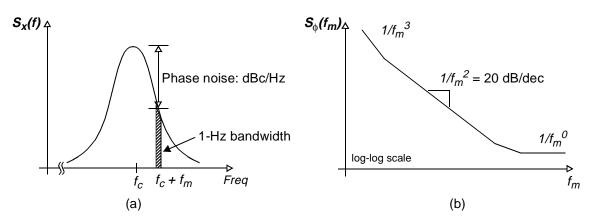

| Fig. 2.15: | Spectral Representations of Phase Noise                             |

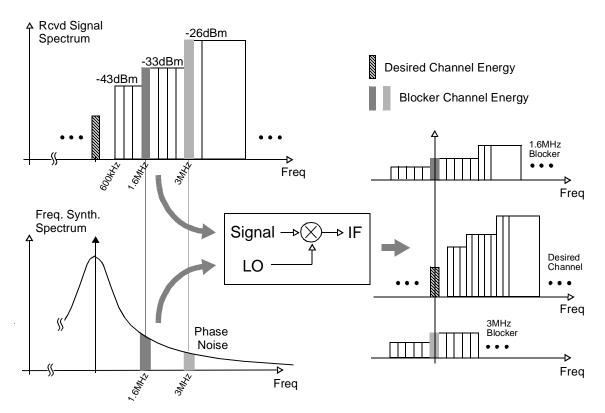

| Fig. 2.16: | Effect of Phase Noise in Wireless Receiver                          |

| Fig. 2.17: | Phase Noise Effect for Direct Conversion Transmitter                |

| Fig. 2.18: | Time and Frequency Representations of Spurious Tones 37             |

| Fig. 2.19: | Effect of Spurious Tones in Wireless Receiver                       |

| Fig. 2.20: | Spurious Tone Effect for Direction Conversion Transmitter 40        |

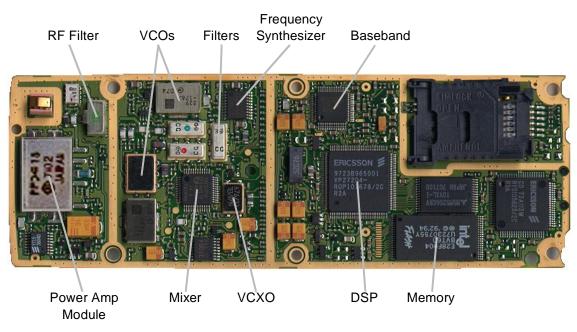

| Fig. 3.1:  | Photograph of Ericsson 788 PCB 45                                   |

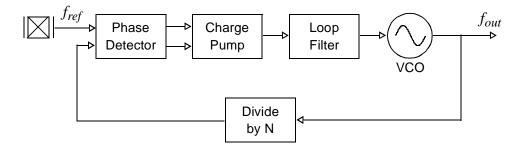

| Fig. 3.2:  | Simplified Block Diagram for Phase-Locked Loop 46                   |

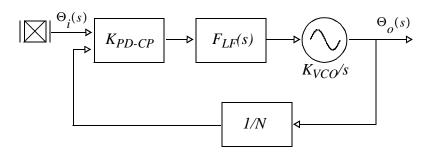

| Fig. 3.3:  | Small-Signal AC Model of PLL                                        |

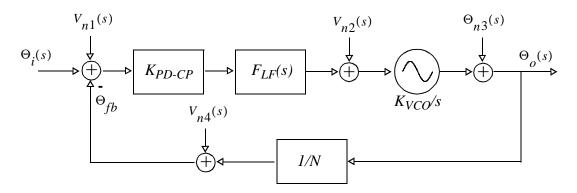

| Fig. 3.4:  | Small-Signal AC Model of PLL with Noise Sources                     |

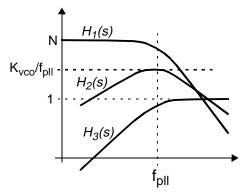

| Fig. 3.5:  | Transfer Functions for Eq. 3 - 7, Eq. 3 - 8, and Eq. 3 - 9 51       |

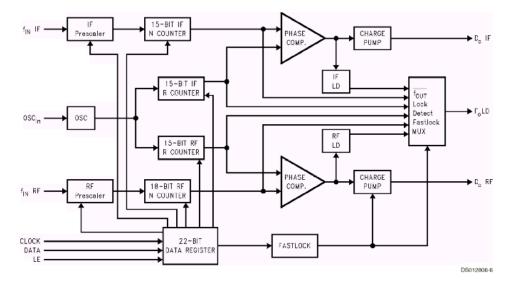

| Fig. 3.6:  | Functional Block Diagram of National Semiconductor LMX2332L. 53     |

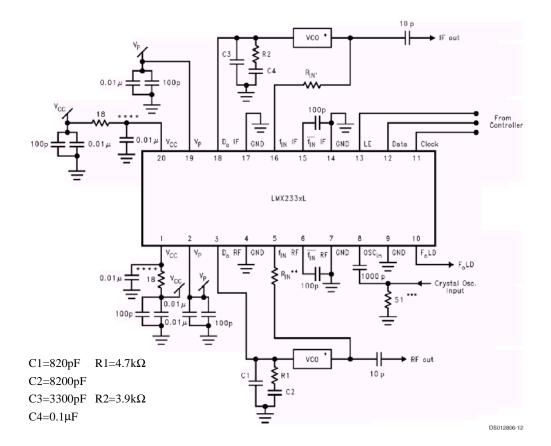

| Fig. 3.7:  | Typical Application of National Semiconductor LMX2332L 54           |

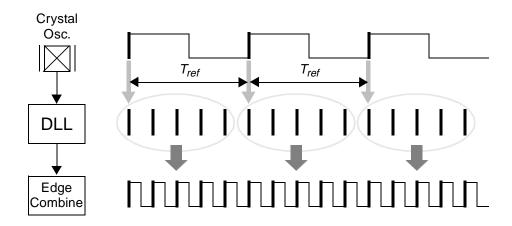

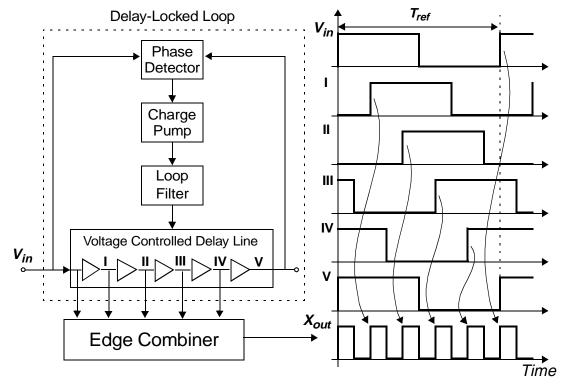

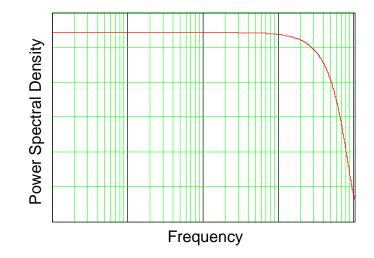

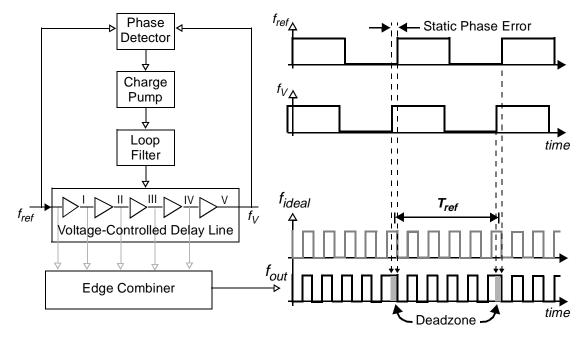

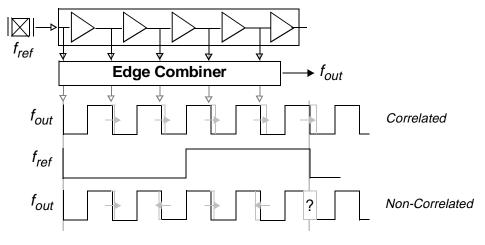

| Fig. 4.1:  | DLL-based Frequency Multiplier Concept                              |

| Fig. 4.2:  | Operation for DLL-based Frequency Multiplier                        |

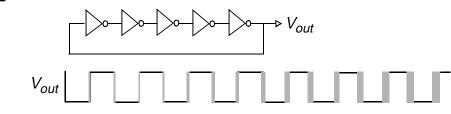

| Fig. 4.3:  | Timing Jitter Accumulation for Ring Oscillator vs. Delay Chain 75   |

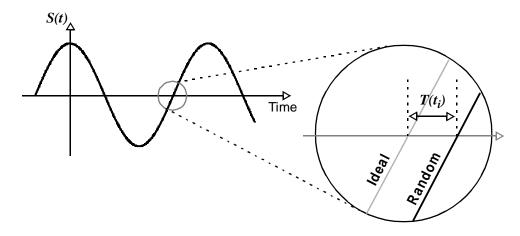

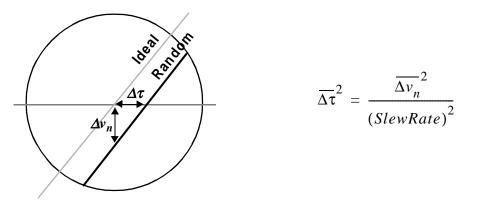

| Fig. 4.4:  | Timing Uncertainties in a Sinusoidal Waveform                       |

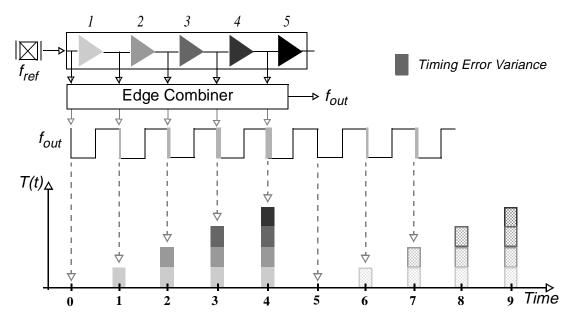

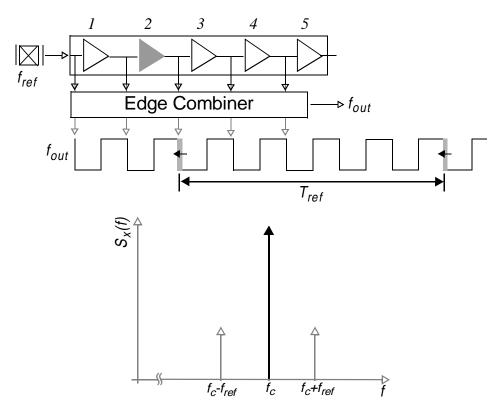

| Fig. 4.5:  | Timing Error Accumulation for Five-Stage Delay Chain                |

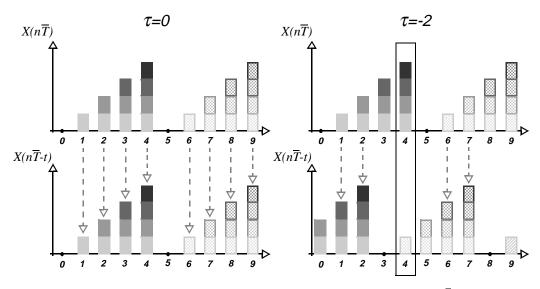

| Fig. 4.6:  | Autocorrelation Operation of Random Process                         |

| Fig. 4.7:  | Autocorrelation of Timing Error Random Process for Five-Delay-Stage |

|            | Example                                                             |

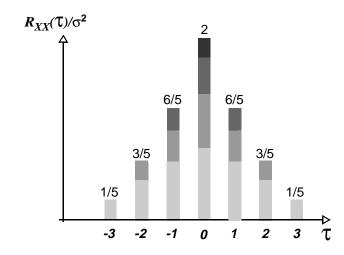

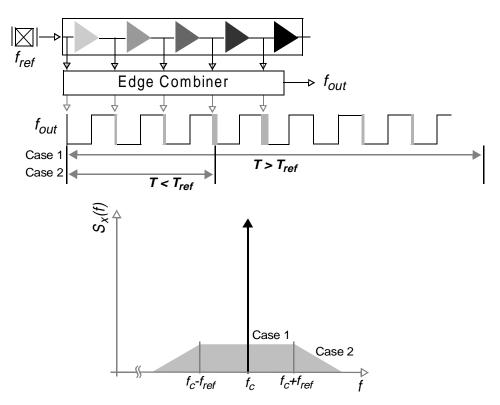

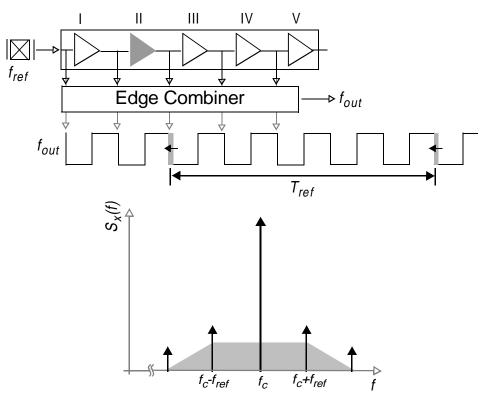

| Fig. 4.8:  | Power Spectral Density for Five Delay Stage Example                 |

| Fig. 4.9:  | Mismatch in Delay Stage                                             |

| Fig. 4.10: | Static Phase Error.                                             | 87  |

|------------|-----------------------------------------------------------------|-----|

| Fig. 4.11: | Phase Noise Plot for Synthesized Delay Output.                  | 91  |

| Fig. 4.12: | Spurious Tones Locations.                                       | 93  |

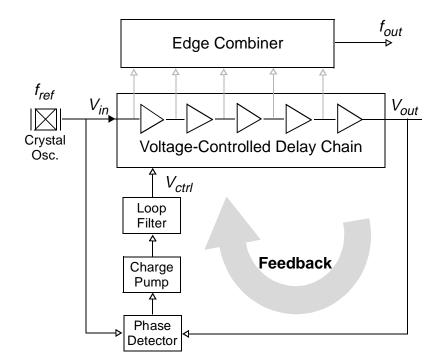

| Fig. 5.1:  | Simplified Block Diagram for Delay-Locked Loop Frequency        |     |

|            | Synthesizer.                                                    |     |

| Fig. 5.2:  | Some possible Transfer Functions for DLL Frequency Synthesizer. |     |

| Fig. 5.3:  | Phase Detector Range.                                           |     |

| Fig. 5.4:  | Two Cases for Phase Detector to Resolve.                        |     |

| Fig. 5.5:  | Small-Signal AC Model of DLL Loop.                              |     |

| Fig. 5.6:  | Correlated vs. Uncorrelated Timing Error.                       |     |

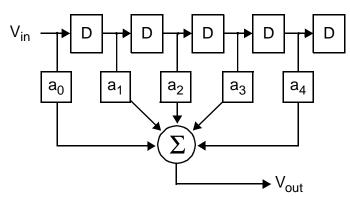

| Fig. 5.7:  | Digital Filter Model for Five-Stage Delay Chain.                | 108 |

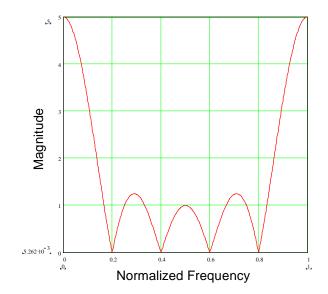

| Fig. 5.8:  | Five-Tap FIR Filter Transfer Function.                          | 109 |

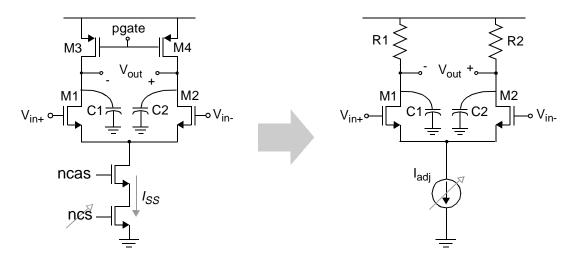

| Fig. 5.9:  | Differential Delay Cell with PMOS Triode Load.                  | 111 |

| Fig. 5.10: | Conceptual Diagram for Replica Bias.                            | 115 |

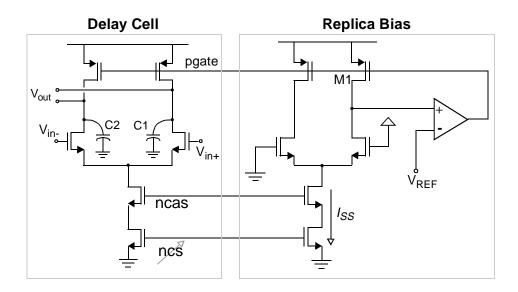

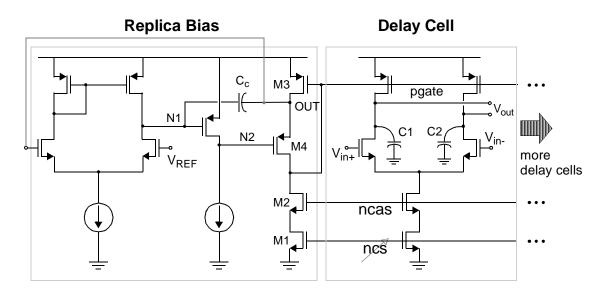

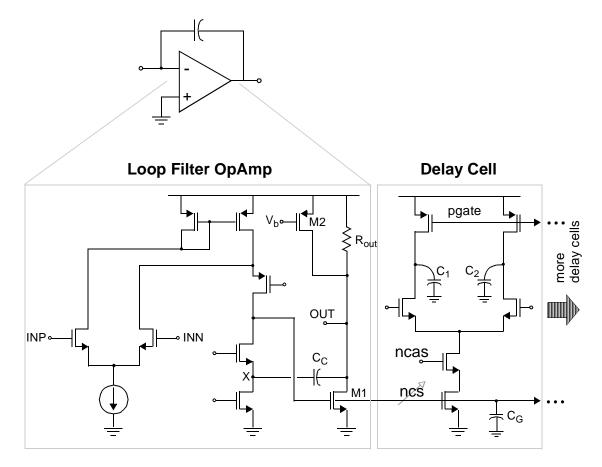

| Fig. 5.11: | Circuit Schematic for Delay Cell and Replica Bias.              | 117 |

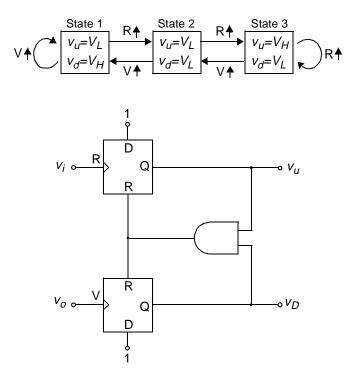

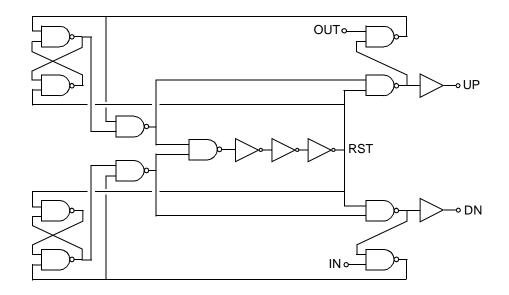

| Fig. 5.12: | Tri-State Phase Detector.                                       | 119 |

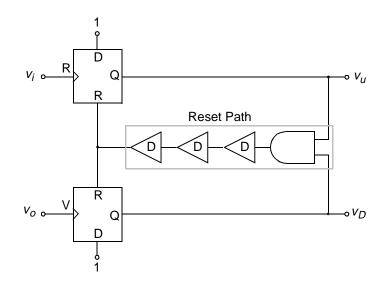

| Fig. 5.13: | Tri-State Phase Detector with Extra Delay in RST Path.          | 120 |

| Fig. 5.14: | Circuit Schematic for Phase Detector.                           | 121 |

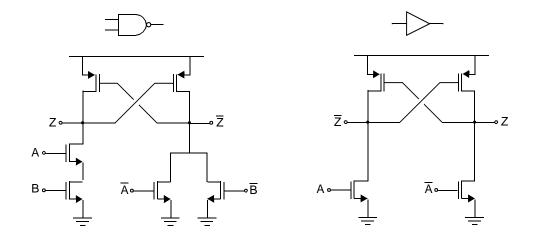

| Fig. 5.15: | DCVSL NOR Gate and Buffer Circuits.                             | 121 |

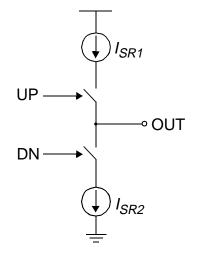

| Fig. 5.16: | Conceptual Circuit Diagram for Charge Pump.                     | 122 |

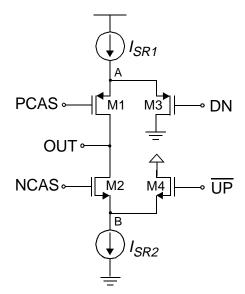

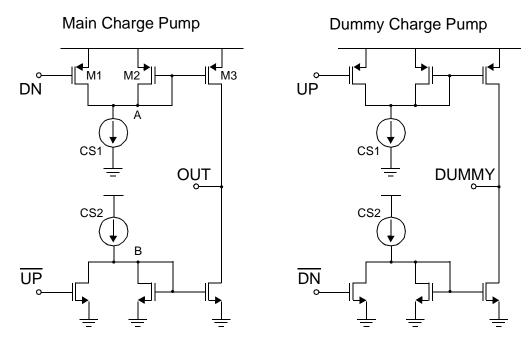

| Fig. 5.17: | Simple Charge Pump Circuit.                                     | 123 |

| Fig. 5.18: | Circuit Schematic for Charge Pump.                              | 124 |

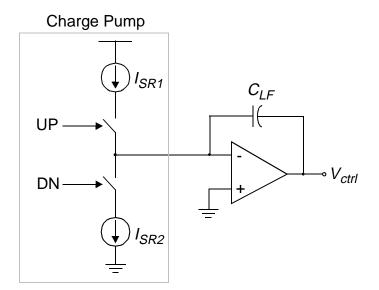

| Fig. 5.19: | Loop Filter Configuration.                                      | 125 |

| Fig. 5.20: | Modified Loop Filter Configuration.                             | 126 |

| Fig. 5.21: | Circuit Schematic for Loop Filter.                              | 127 |

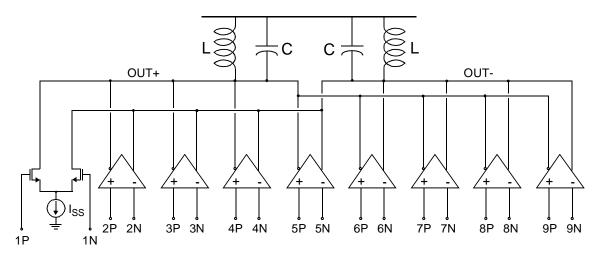

| Fig. 5.22: | Circuit Schematic for Edge Combiner (N=9).                      | 128 |

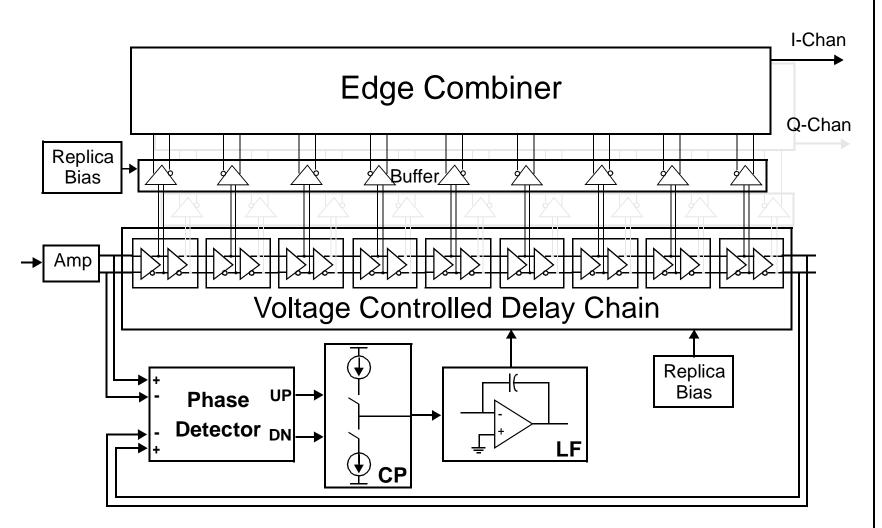

| Fig. 6.1:  | Chip Implementation Block Diagram.                              | 137 |

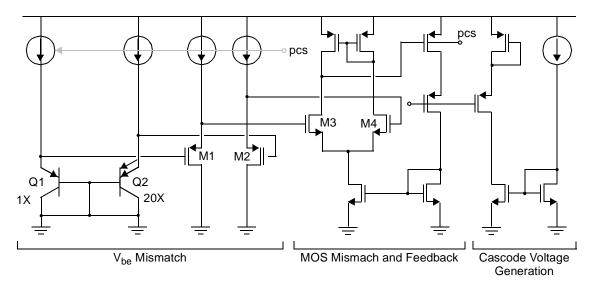

| Fig. 6.2:  | Circuit Schematic for Master Bias.                              | 139 |

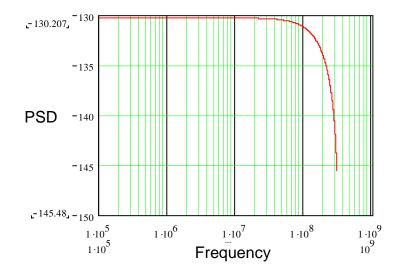

| Fig. 6.3:  | Phase Noise Prediction.                                         | 141 |

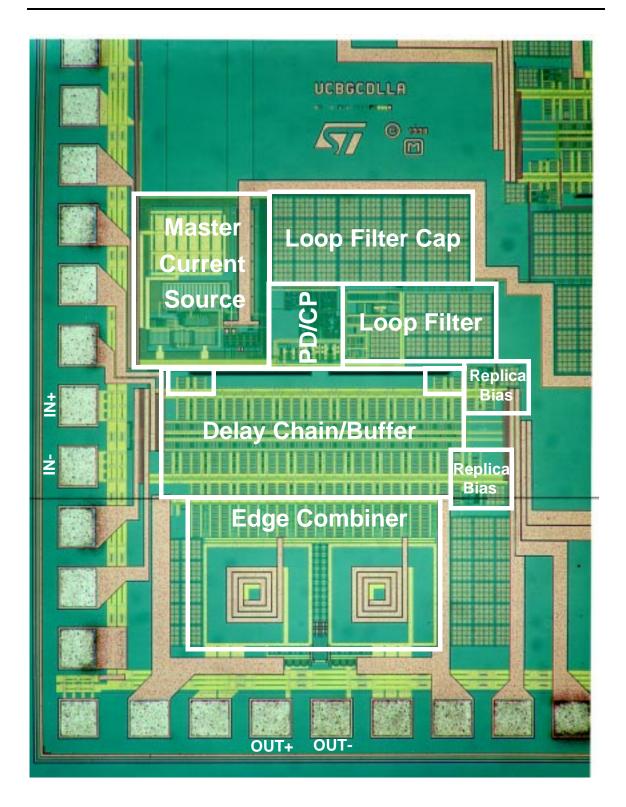

| Fig. 6.4:  | Die Micrograph.                                                 | 143 |

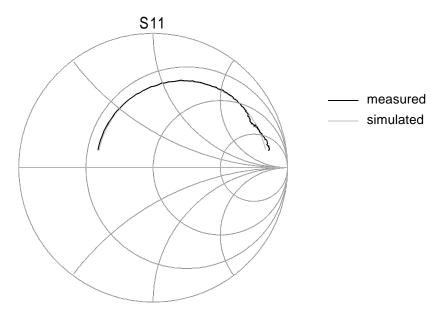

| Fig. 6.5:  | S11 for Spiral Inductors.                                       | 146 |

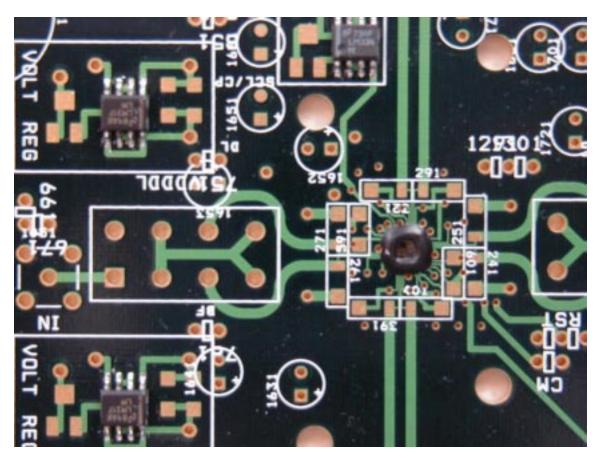

| Fig. 7.1:  | Photograph of Chip-On-Board Area.                               | 150 |

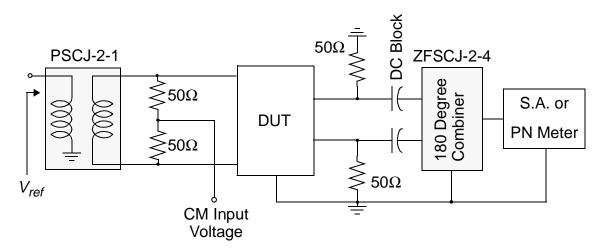

| Fig. 7.2:  | Test Setup.                                                     | 151 |

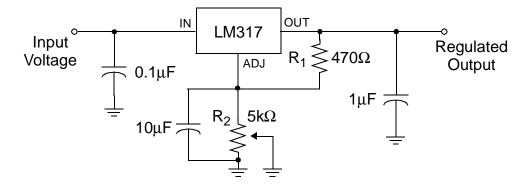

| Fig. 7.3:  | Voltage Regulator Configuration.                                | 152 |

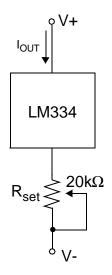

| Fig. 7.4:  | External Current Source Configuration.                          | 152 |

| Fig. 7.5:  | Single Sideband Phase Noise Plot with IS-137 Requirements.      | 155 |

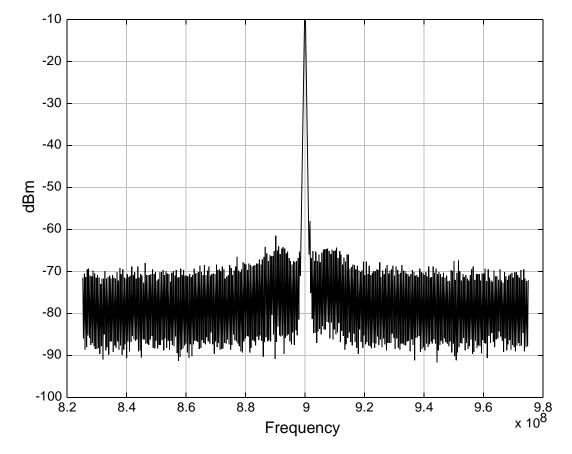

| Fig. 7.6:  | Output Spectrum Plot.                                           |     |

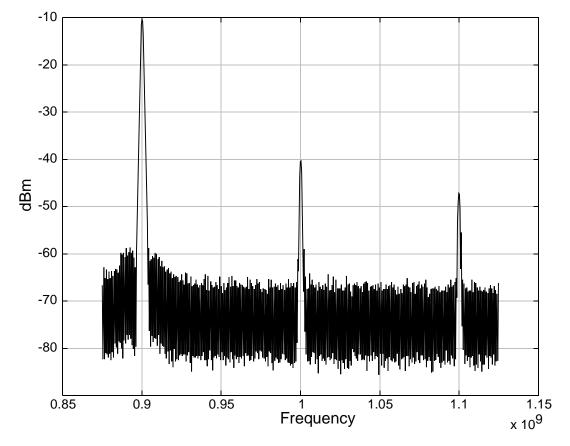

| Fig. 7.7:  | Spurious Tone Plot.                                             | 157 |

|            |                                                                 |     |

| Fig. 7.8: | Comparison of Recently Published Integrated VCO/PLLs. | 159 |

|-----------|-------------------------------------------------------|-----|

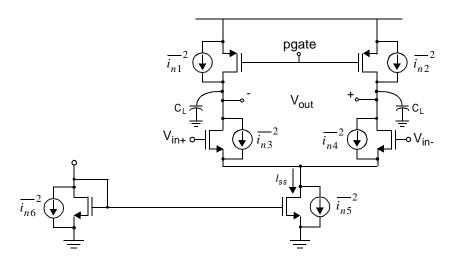

| Fig. A.1: | Differential Delay Stage with Thermal-Noise Sources   | 165 |

| Fig. A.2: | Differential Delay Cell with PMOS Triode Load         | 166 |

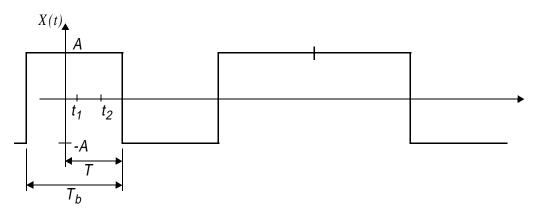

| Fig. B.1: | A Sample Function of the Random Binary Waveform       | 173 |

# Acknowledgements

It has been a great privilege to be a graduate student in the EECS department at the University of California, Berkeley, and certainly a grand finale for all the years that I have been in school. My experience here is full of opportunities to learn not only from faculties and students that are experts in the field, but also from the interactions with sponsoring companies and industrial fellows with expertise in the marketplace. In addition, family and friends outside of the department have also been an important part of my life. Therefore, I would like to directly thank those people who are particularly instrumental in contributing to my experience at UC Berkeley.

First and foremost, I would like to thank my advisor, Professor Paul R. Gray, for his invaluable guidance throughout my graduate career. His wealth of knowledge in the integrated circuit and system designs have assisted me in identifying the critical and interesting issues of research. His attitude toward work and professionalism have inspired me to continuously challenge myself to reach new levels. I look up to him not only as an excellent research advisor, but also a great human being. It has certainly been an unique privilege to be a member of the PRG group, and I hope to carry on the tradition of excellence in the future work place.

I would also like to thank other faculties in the department who have contributed in different parts of my graduate school experience: Professor Meyer, Professor Boser and Professor Brodersen for technical discussions and being great lecturers for Analog Integrated Circuit courses (best of its kind); Professor Kahn and Professor Wright (from Mechanical Engineering Dept.) for being in my Qual committee and reviewing my thesis; Professor Anantharam and Professor Tse for discussions in random process. One of the best things about the graduate school has been the talented and interesting people that I have had the privilege to work and become friends with. Many thanks to Thomas Cho who was my mentor for Masters work in the area of Pipelined ADC and a great friend to talk to. A special thanks to Todd Weigandt whose Ph.D. research was the basis of my thesis topic and has given me great advises in the foundation and direction of my research. Other senior graduate students in the group, Cormac Conroy, Greg Uehara, Ken Nishimura, Robert Neff, Dave Cline and many others, have helped me to find my ways around the department and also technical assistance during my early years of graduate school. For the past several years, I wish to thank Jeff Ou, Chris Rudell for being great partners on the DECT project and good friends outside of Cory; Keith Onodera, Andy Abo, Sekhar Narayanaswami and Jeff Weldon for offering their knowledge in technical and non-technical fields. In more recent years, I'd like to thank Martin Tsai, Luns Tee and Li Lin for technical discussions and being great cubical-mates. I wish them a speedy graduation.

Last in the research area, I would like to thank STMicroelectronics for fabrication support, as well as sending four wonder industrial fellows to work with us on two generations of transceiver projects: Francesco Brianti, Marco Sabatini, Danilo Gerna, Sebastien Dedieu and become good friends with us; National Semiconductor - Wireless Communication Group for test support; MSG staff in 558 Cory Hall, Diane Chang and Carol Sitea - who have been a firefighter in many emergency cases, Elise Mills for being a wonderful Grant Administrator.

I am also greatly indebted to my family who have supported me throughout the years. Coming to the US at the age of 15 is not entirely an easy task both for myself and

my parents. I really appreciate my parents, Dr. Chiu-Yuan Chien and Mrs. Ming Hsu Chien, my brother, Tun-Cheng Chien, who have patiently listened to my complains during the tough times and cheered with me during the good times. My best wish to my brother who is currently working toward his doctoral degree at the University of Michigan, Ann Arbor and my sister-in-law who is expecting their first baby. I'd also like to thank many other relatives who have also been very supportive during the years since my arrival to the US.

Finally, I am grateful to my fiancee-to-be, Angela Yen-Chun Chou, for her love and patience in the past few years as I worked day and night, weekdays and weekends to complete my studies here at Berkeley. I am very fortunate to have her as a very good friend and a future companion.

All-in-all, my experience at Berkeley has been tremendous. For people who have graduated from this department or the PRG group, I am sure that you would agree with me. For those who are currently working toward a degree, you may not see the fruit of your efforts at the moment, but I can assure you that it will come. For those who are interested in UC Berkeley for graduate school, I encourage you to consider it seriously.

My acknowledgements would not be complete without expressing my gratitude towards God. I feel very fortunate to come to know Him during my undergraduate years at UCLA and have continually been blessed by His endless love ever since. He is the true shepherd of my life.

This project was supported by the Defense Advanced Research Projects Agency, the California MICRO and National Science Foundation #CCR-9732550. **Chapter 1**

# Introduction

### **1.1 Motivation**

The market for wireless communication has grown explosively in recent years with the fast development of new products and services. Current devices on the market, such as cordless/cellular telephones, wireless LAN's, and GPS/satellite receivers, utilize the frequency spectrum between 800 *MHz* to 2.5 *GHz* for communication. As technology advances, today's savvy consumers demand wireless systems that are low-cost, low-power and with a small form-factor. Therefore, much recent effort in circuit design for wireless systems has been devoted to the design of a single-chip transceiver implemented in the low-cost CMOS technology [1][2]. This requires researches in new transceiver architectures and circuit design techniques that will enable a fully integrated RF transceiver. One of the key components in the integrated RF transceiver is the frequency synthesizer, whose main functions are to provide a precise carrier frequency for the local oscillator and to supply the accurate timing information for the sampling circuits in baseband (i.e., switched capacitor filter and analog-to-digital converter). This dissertation focuses on the new design technique of a DLL-based frequency multiplier that is used as the local oscillator for wireless applications.

To achieve optimal system performance, the following two factors are essential: precise frequency generation for local oscillators in communication systems, and accurate timing-edge generation for sampled-data circuits in baseband. For most communication systems, a reference crystal oscillator either provides the required timing information or functions as a reference for a frequency synthesis block, such as a Phase-Locked Loop. Therefore, minimizing the *additive* timing error (noise introduced in the active circuit block) is the primary task in the design. In some systems, timing information and data are recovered from a corrupted signal (for example, local area network, ADSL, fiber-optic link, etc. [3][4][5]); in this case, low-jitter timing generation is desirable.

Two main types of timing uncertainties are critical in communication systems: timing jitter and spurious tones. Timing jitter is the random timing fluctuation of clock edges in the time domain. In a sampled-data application, random timing fluctuation affects the timing accuracy of the sampled data. Spurious tones are periodic timing fluctuations of clock edges in the time domain. In a wireless transmitter application, spurious tones in a local oscillator create undesired spectral emissions at undesired frequencies. Many sources of errors that are present in actual implementations of the system may also affect the timing uncertainties, including supply variation, substrate coupling, etc. In most wireless communication systems, information is modulated and transmitted at a much higher frequency than the signal bandwidth, commonly known as the carrier frequency. A precise frequency synthesizer, usually implemented with a *Phase-Locked Loop* (PLL), is used to generate the carrier frequency. To maximize the spectral usage and optimize performance within the available bandwidth, timing uncertainties (both random and periodic) need to be minimized. Conventionally, the *Voltage-Controlled Oscillator* (VCO) in a PLL is implemented with an external resonator, such as a LC-tank. An external resonator is generally of very high quality, which minimizes noise contributions. However, with the reduction of the external component count and an increasing level of integration for RF transceivers, the selectivity and sensitivity are often compromised by using integrated VCOs.

Already present in today's clock/data recovery systems (such as disk drive read channels and 10/100Base-T LAN applications), an on-chip ring-oscillator [6] and a volt-age-controlled delay line [7][8][9] have resulted in a higher integration and lower cost solution than discrete component implementations. An increasing number of research publications employ various VCO and synthesizer design techniques to target radio applications [6][10][11][12][13][14]. However, because the phase noise requirement of wire-less systems is generally more difficult to achieve, integrated VCOs and synthesizers may not be useful for RF frequency synthesis without new design techniques that improve their performance.

### **1.2 Research Goals**

This research addresses the issues regarding the local oscillator integration in CMOS for wireless applications, and investigates the use of a DLL-based frequency multiplier as a local oscillator to avoid the timing jitter accumulation in oscillators. Detailed analysis is given to estimate the phase noise performance of the DLL-based frequency multiplier; in addition, CMOS design techniques of the local oscillator are also presented. For demonstration purposes, an experimental prototype based on the analysis of this research is designed to meet the specification of IS-137 cellular telephone standard [15]. This system, commonly known as the AMPS/TDMA system, is widely available throughout the world. Due to the narrow channel spacing of 30kHz, this standard represents one of the more difficult phase noise specifications in wireless systems.

The key contributions of this work are:

- A DLL-based frequency multiplier whose timing jitter does not accumulate from cycle-to-cycle, and whose noise performance is independent of the low quality factor of on-chip spiral inductors.

- An analytical model that describes the timing jitter and phase noise performance of the DLL-based frequency multiplier, taking into consideration the thermal-noiseinduced jitter performance of CMOS differential source-coupled delay cells with PMOS triode-region loads.

- The application of the DLL-based frequency multiplier analysis to a monolithic CMOS low-phase-noise local oscillator for cellular telephone applications.

Experimental results for the DLL-based frequency multiplier local oscillator fabricated in a 0.35µm double-poly 5-metal CMOS process, which show a very good agreement with the analytical predictions for phase noise and spurious tones.

#### **1.3 Thesis Organization**

Chapter 2 begins with a review of receiver and transmitter architectures. In particular, several integration-friendly architectures are discussed in detail with design trade-offs for different functional blocks. The role of frequency synthesizers in wireless communication systems for both receivers and transmitters is then introduced. The two key non-idealities for frequency synthesizers, namely *phase noise* and *spurious tones*, are discussed with their impacts on receiver and transmitter performance.

Chapter 3 begins with a brief review of Phase-Locked Loop (PLL) fundamentals as well as the key design equations of a PLL, followed by an overview of recent publications on integrated Voltage-Controlled Oscillators (VCO). This chapter concludes with a proposal of a new local oscillator architecture that addresses the two main issues that limit the performance of monolithic VCO implementations.

Chapter 4 introduces the basic operation of the DLL-based frequency multiplier and the concept to achieve low phase noise performance. Phase noise, caused by thermalnoise-induced timing error in delay cells, is carefully studied, and a mathematical model that characterizes the noise behavior is presented. Spurious tones, mainly due to mismatch in design, are also studied. These characteristics are taken into consideration in wireless system designs.

Chapters 5 and 6 detail the implementation specifics for the DLL-based frequency multiplier block transfer function, system equation, circuit design and prototype implementation. This is followed by Chapter 7 which presents the target application and measurement results. Finally, the conclusions are presented in Chapter 8.

### **1.4 References**

- Paul R. Gray, and Robert R. Meyer, "Future Directions in Silicon ICs for RF Personal Communications," *Proceedings*, 1995 Custom Integrated Circuits Conference, pp. 83-90, May 1995.

- [2] A. A. Abidi, A. Rofougaran, G. Chang, J. Rael, J. Chang, M. Rofougaran, and P. Chang, "The Future of CMOS Wireless Transceivers," *Digest of Technical Papers, International Solid-State Circuit Conference*, pp. 118-119, San Francisco, 1997.

- [3] B. Kim, D. Hellman, and P. R. Gray, "A 30MHz Hybrid Analog/Digital Clock Recovery Circuit in 2mm CMOS," *IEEE J. Solid-State Circuits*, vol. 25, no. 6, pp.1385-1394, Dec. 1990.

- [4] T. Hu, P. R. Gray, "A Monolithic 480Mb/s parallel AGG/decision/clock-recovery circuit in 1.2 μm CMOS," *IEEE J. Solid-State Circuits*, vol. 28, no. 12, pp.1314-1320, Dec. 1993.

- [5] M. Soyuer, "A Monolithic 2.3-Gb/s 100-mW Clock and Data recovery Circuit in Silicon Bipolar Technology," *IEEE J. Solid-State Circuits*, vol. 28, no. 12, pp. 1310-1313, Dec. 1993.

- [6] S. Lee, B. Kim, K. Lee, "A Fully Integrated Low-Noise 1-GHz Frequency Synthesizer Design for Mobile Communication Application," *IEEE J. Solid-State Circuits*, vol. 32, no. 5, pp. 760-765, May, 1997.

- [7] T. Lee, K. Donnelly, J. Ho, J. Zerbe, M. Johnson, T. Ishikawa, "A 2.5V CMOS Delay-Locked Loop for an 18 Mbit, 500Megabytes/s DRAM," *IEEE J. Solid-State Circuits*, vol. 29, no. 12, pp. 1491-1496, Dec. 1994.

- [8] J. Maneatis, "Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques," *IEEE J. Solid-State Circuits*, vol. 31, no. 11, pp. 1723-1732, Nov. 1996.

- [9] A. Efendovich, Y. Afek, C. Sella, Z. Bikowsky, "Multifrequency Zero-Jitter Delay Locked Loop," *IEEE J. Solid-State Circuits*, vol. 29, no. 1, pp. 67-70, Jan. 1994.

- [10] J. Craninckx, M. S. J. Steyaert, "A 1.8-GHz CMOS Low-Phase-Noise Voltage-Controlled Oscillator with Prescaler," *IEEE J. Solid-State Circuits*, vol. 30, no. 12, pp. 1474-1482, Dec. 1995.

- [11] J. Craninckx, M. S. J. Steyaert, "A 1.8-GHz Low-Phase-Noise CMOS VCO Using Optimized Hollow Spiral Inductors," *IEEE J. Solid-State Circuits*, vol. 32, no. 5, pp. 736-744, May, 1997.

- [12] C. H. Park, B. Kim, "A Low-Noise, 900-MHz VCO in 0.6-µm CMOS," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 586-591, May, 1999.

- [13] J. Y-C. Chang, A. A. Abidi, and M. Gaitan, "Large Suspended Inductors on Silicon and their use in a 2-µm CMOS RF Amplifier," *IEEE Electron Device Letters*, vol. 14, pp. 246-248, May 1993.

- [14] A. Rofougaran, J. Rael, M. Rofougaran, and A. A. Abidi, "A 900 MHz CMOS LC-Oscillator with Quadrature Outputs," *Digest of Technical Papers, International Solid-State Circuit Conference*, pp. 392-393, San Francisco, 1996.

- [15] EIA/TIA Standard, "Cellular System Dual-Mode Mobile Station Base Station Standard, IS-137A," *Telecommunications Industry Association*.

## Chapter 2

# Frequency Synthesizer in Wireless Communication Systems

### 2.1 Introduction

There are many different types of wireless communication systems on the market today, ranging from cordless and cellular telephones for voice to wireless local area network for data. A sample list of existing wireless communication systems is shown in Table 2-1 along with their key parameters. Although these systems differ from each other in many different ways (i.e. carrier frequency, channel spacing, modulation format, etc.), they all contain a RF functional block to modulate and demodulate the transmitted and received signals.

Different from the "wired" communication counterpart, all wireless applications have two common characteristics: they share the same medium - electromagnetic waves through the air interface - and they all operate in a passband around a carrier frequency. The carrier frequency of recently developed wireless applications tend to increase as the spectrum becomes more crowded. The electromagnetic wave received by antennas consists of many signals for different applications (including broadcasting radio and TV chan-

| Parameter               | AMPS           | IS-54           | GSM            | DECT          | 802.11     |

|-------------------------|----------------|-----------------|----------------|---------------|------------|

| Origin                  | EIA/TIA        | EIA/TIA         | ETSI           | ETSI          | IEEE       |

| Access                  | FDD            | FDM/FDD/TDM     | FDM/FDD/TDM    | FDM/TDM/TDD   | FH/FDM     |

| Modulation              | FM             | π/4 QPSK        | GMSK, diff     | GFSK          | (G)FSK     |

| Data Rate /<br>Channel  | n/a            | 48 kb/sec       | 270.8 kb/sec   | 1.152 Mb/sec  | 1-2 Mb/sec |

|                         |                | (2 bits/symbol) |                |               |            |

| RF Channel<br>Frequency | 824-848MHz(Tx) | 824-848MHz(Tx)  | 890-915MHz(Tx) | 0:1897.344MHz | 2.4-2.5GHz |

|                         | 869-893MHz(Rx) | 869-893MHz(Rx)  | 935-960MHz(Rx) | 9:1881.792MHz |            |

| Number of RF            | 833            | 833             | 124            | 10            | 75         |

| Channels                |                |                 |                |               |            |

| Channel Spacing         | 30kHz          | 30kHz           | 200kHz         | 1.782MHz      | 1MHz       |

**TABLE 2-1** Summary of Wireless Communication Standards

nels, military information, aeronautical and maritime communication). For the wireless *receiver*, the desired information is only a very small part of this broad spectrum of received signal; as a result, it is inherently difficult to extract the desired information. To maximize the bandwidth usage, higher carrier frequencies and more stringent spectrum restrictions to prevent interference among different wireless applications are used. At the other end, the wireless *transmitter* processes only the desired information and transmits that at RF frequency; therefore, its specification is much more relaxed.

The receiver's RF block is generally characterized by its sensitivity and selectivity. Sensitivity is a measure of the smallest input signal the RF receiver can detect while maintaining a minimum Signal-to-Noise Ratio (SNR) for a given Bit-Error-Rate (BER). Selectivity refers to the receiver's ability to demodulate a weak desired signal with a given BER in the presence of large adjacent-channel signals. Although sensitivity is primarily determined by the noise performance of the RF front-end circuits, and selectivity is largely affected by the channel select filter at IF or baseband circuits, both performance measure-

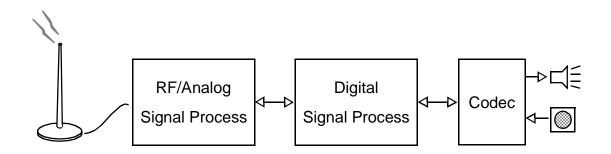

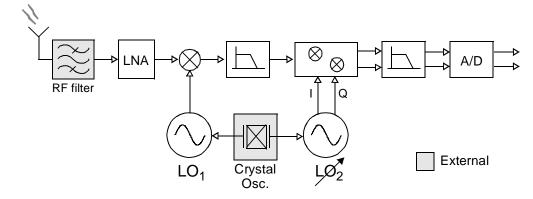

Fig. 2.1: Conceptual Block Diagram for Wireless Transceiver.

ments are also influenced by the quality of the frequency synthesizer. This chapter begins with a review of receiver and transmitter architectures with an emphasis on integration, followed by a discussion of the impact of frequency synthesizers' non-idealities on the receiver and transmitter architectures. Examples of commercial standards are given for illustration.

### 2.2 Receiver Architecture

Fig. 2.1 shows a conceptual block diagram of a transceiver for a cordless or cellular telephone. In the receive path, the RF signal is first received at the antenna and then passed through a series of RF/analog signal processing functions in which the RF signal is down-converted, amplified, filtered and digitized. The digital output is then processed by the Digital Signal Processing (DSP) block which may include digital filtering, demodulation, and error correction. The codec accepts the DSP output and drives an ear piece or speaker on the telephone.

Since the receiver design is inherently more difficult, this section will focus on the receive path of the RF/Analog Signal Processing block. Several different receiver architectures exist today and can be categorized into four distinct groups: *Superheterodyne*, *Direct Conversion*, *Low-IF* and *Wideband IF with Double Conversion*. Later sub-sections describe the characteristics of each architecture and their impacts on the receiver performance. Most importantly, the potential of each receiver architecture for integration will be presented.

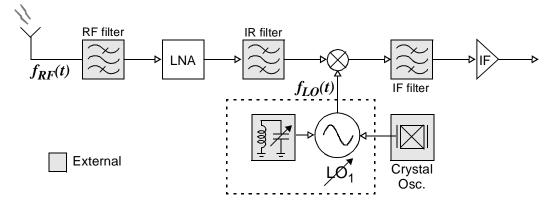

#### 2.2.1 Superheterodyne

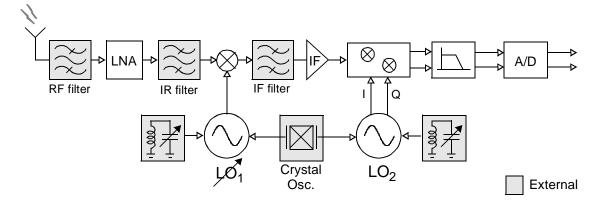

The most commonly used receiver architecture today is the *Superheterodyne* architecture. This architecture was first proposed by E. H. Armstrong in 1917 (U.S. Patent) [16]; because of its superior performance, it has been widely used in various different types of radio applications. Fig. 2.2 shows a simplified block diagram of the superhetero-dyne receiver.

In the superheterodyne receiver architecture, the received RF signal is first passed through the external RF filter which attenuates the out-of-band blocker signals. Then the RF signal is amplified by the Low Noise Amplifier (LNA). It is important to amplify the RF signal at an early stage to increase the signal level and to minimize the impact of noise contributions from later circuit blocks. The amplified signal is then passed through an external Image Reject (IR) filter, typically one with the same characteristics as the RF filter, to further attenuate out-of-band signal and noise, in particular the signal energy in the image band<sup>1</sup>. The first local oscillator (LO) is a variable frequency synthesizer which gen-

Fig. 2.2: Superheterodyne Receiver Block Diagram.

erates a channel-select RF frequency. Together with the first mixer, the first LO down-converts the desired RF channel frequency to a fixed Intermediate Frequency (IF).

The IF signal then goes through an external high-Q channel-select bandpass filter (IF Filter) which rejects most of the adjacent-channel energy and passes the desired channel to an IF amplifier. The second local oscillator generates a fixed IF frequency and down-converts the desired channel at IF to baseband with the second mixer. At baseband, the desired channel goes through the final analog signal processing which may include filter-ing, phase compensation, equalization and digitalization.

This architecture enjoys an excellent sensitivity and selectivity performance due to the presence of discrete high-Q filters. The RF and IR filters significantly reduce the unwanted signal energy from the image band that would potentially degrade the sensitiv-

<sup>1.</sup> After down conversion, the image band signal energy coincides with the desired signal energy, degrading the Signal-to-Noise Ratio (SNR). Careful choice of IF frequency ensures sufficient attenuation in the image band by both RF and Image Filters.

ity. The high-Q channel-select bandpass filter attenuates the adjacent channel energy and increases the selectivity performance by orders of magnitude. However, these external filters are expensive and prohibit the full integration of the receiver.

From the frequency synthesizer point of view, the first local oscillator generates a channel-select RF frequency which is required to synthesize channel frequencies in small frequency steps. Because of the loop dynamics, this frequency synthesizer needs to have a small loop bandwidth which does not provide the VCO phase noise suppression (will be discussed in detail in Chapter 3). In the superheterodyne receiver architecture, the VCO is generally implemented with high-Q external components which provides excellent phase noise performance. However, using external components prevents full integration of receiver. Recent examples of superheterodyne designs can be found in [17][18][19][20].

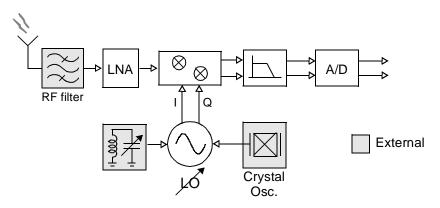

#### **2.2.2 Direct Conversion (Zero-IF)**

One step toward full receiver integration would be to remove the external high-Q filters that are present in the superheterodyne architecture. Shown in Fig. 2.3 is the conceptual block diagram of the *Direct Conversion* receiver architecture (also known as Zero-IF or ZIF architecture). It consists of only one external RF filter in the receive path. This receiver topology is commonly used in pager or two-way radio applications where the performance requirement is relaxed. A recent publication suggests that this architecture can also be used for cordless telephone applications with moderate performance requirements [21].

Fig. 2.3: Direct Conversion Receiver Block Diagram.

As in the superheterodyne architecture, the received RF signal is first filtered by the RF filter which attenuates the out-of-band blocker signals, and then the signal is amplified by a LNA. The local oscillator is a variable frequency synthesizer whose output is centered at the desired channel frequency. Together with the mixer, the LO signal down-converts the RF signal directly to baseband with the desired channel located at DC. Due to the direct conversion of RF signal, no image band is present; this eliminates the need for the IR filter in the superheterodyne architecture. In addition, no external IF filter is required since there is no IF frequency. At baseband, the signal is then amplified and filtered by continuous time filters and digitized by an Analog-to-Digital Converter (ADC) for further Digital Signal Processing (DSP).

In the direct conversion receiver, prior to the input of baseband circuits, the only filter present is the RF filter which attenuates energy from out-of-band RF signals. Adjacent channel energy relative to the desired channel remains unchanged at the baseband input. Since the channel-select IF filter has been removed from the receive path for integration, the possible presence of the large adjacent channel energy with a small desired channel signal translates to a stringent linearity requirement for the baseband filter and ADC circuits [22][23]. Therefore, the sensitivity and selectivity performance of a direct conversion receiver largely depends on the design complexity of the RF and baseband circuit blocks.

In addition to the adjacent channel energy problem, other system non-idealities need to be overcome to achieve full integration. Two error sources contribute to the DC offset in the receive path. First, the local oscillator output in the direct conversion receiver centers at the desired channel frequency. A small amount of LO energy may be radiated and then received by the antenna, and it can be self-mixed down to baseband as a DC component. Due to the nature of direct conversion receiver where the gain in front of baseband is limited, the DC offset due to LO leakage can be much larger than the desired channel energy, hence saturating the desired signal. Secondly, the limited gain before the baseband circuits increases the offset requirement of later circuit blocks. As a result, the DC offsets, along with other error sources (i.e. 1/f noise) must be removed with careful circuit design techniques or an adaptive feedback system.

As in the superheterodyne receiver, the local oscillator generates a RF frequency which needs to increment in small frequency steps. In order to achieve low noise performance with a small PLL bandwidth, an external VCO is commonly used. This prohibits the full integration of the receiver.

Fig. 2.4: Low-IF Receiver Block Diagram.

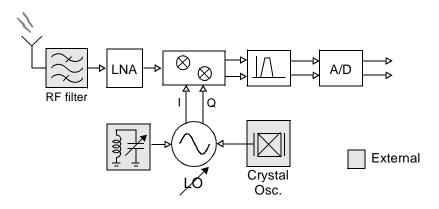

### 2.2.3 Low-IF Architecture

One way to avoid the DC offset and 1/f noise problems in the direct conversion or ZIF receiver is to place the down-converted signal away from DC. Shown in Fig. 2.4 is the block diagram for a *Low-IF* receiver topology. The RF section is identical to the ZIF receiver where no discrete filter, except the RF filter, is used in the receive path. The local oscillator frequency is deliberately selected to be slightly away from the desired channel frequency, so the down-converted desired channel will be centered at a frequency that is equal to the difference between the frequencies of the local oscillator and the desired channel. An integrated bandpass filter can be used at this frequency to perform channel selection.

This topology eliminates the DC offset and 1/f noise problems of the direct conversion architecture by down-converting the desired signal to a frequency away from DC. However, in addition to the integrated RF channel-select frequency synthesizer issue mentioned in previous two architecture examples, the low-IF topology needs to reject close-in image energy. The down-converted desired channel is typically above DC, but low enough to ease the implementation of baseband bandpass filter. However, this creates a new problem of rejecting nearby image energy (typically a few hundred kHz away), much closer than the image rejection band in a conventional superheterodyne receiver (typically tens of MHz away). The conventional image band is strongly attenuated by the RF and IR filters in the superheterodyne receiver architecture, reducing its effect on the receiver performance. Because the nearby image energy in the Low-IF receiver cannot be filtered by the front-end RF filter, active image reject mixer techniques are required for this architecture [24]. However, active image reject mixers generally achieve a limited image rejection due to local oscillator I/Q phase and gain mismatches. Similar to the nearby image energy issue mentioned above, the specified blocker energy can also be down-converted to a frequency closer to the desired channel than the original blocker location. This increases the difficulty of designing the channel-select filter. Furthermore, the complexity of the integrated bandpass filter increases as the channel bandwidth increases due to the additional poles and zeros needed to implement the bandpass filter function versus lowpass filtering. Also, the power dissipation required for a wide bandwidth may prohibit a full integration. Therefore, because of the nearby image and blocker energy, and integrated bandpass filter issues, the low-IF architecture is suitable only for communication systems where the nearby image and blocker energy is small and the channel bandwidth is relatively narrow. An example of a low-IF receiver can be found in [25].

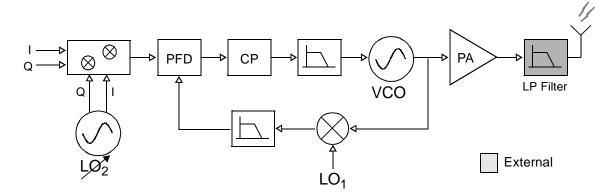

#### 2.2.4 Block-Down Conversion: Wideband IF with Double Conversion

The three receiver architectures above all use a RF frequency synthesizer to perform the channel selection function. This requires the frequency synthesizer to generate LO frequencies in small frequency steps corresponding to the channel bandwidth. Due to the limitation of PLL transfer functions, this implementation requires high-Q external VCOs to achieve the required noise performance for wireless communication systems. One technique which may enable a fully-integrated receiver architectures is block down-conversion.

Block down-conversion technique utilizes a fixed-frequency first local oscillator  $(LO_1)$  to down-convert the entire RF band to IF. This technique may potentially eliminate the need for discrete IR and IF filters in the superheterodyne architecture, and allows new explorations of low-noise  $LO_1$  design that only needs to generate a fixed frequency. One example for this approach is the *Wide-band IF with Double Conversion* (WBIFDC). This architecture also addresses some of the issues mentioned in previous sections.

Shown in Fig. 2.5 is a simplified block diagram for WBIFDC [26][27]. This topology requires no external components in the receive path, with the exception of the RF filter to attenuate out-of-band signals. It employs active image-reject mixers to reduce the image band energy. DC offset caused by LO self-mixing is eliminated by using two LO's centered at frequencies different from the carrier frequency.

Fig. 2.5: Wideband IF with Double Conversion Receiver Block Diagram.

The received RF signal is first filtered by the RF filter and amplified by the LNA. Together with the first *fixed-frequency* local oscillator, the mixer down converts the entire received RF signal to an IF frequency where a simple RC lowpass filter attenuates higher order terms due to mixing. The second set of mixers, together with the second local oscillator tuned to the desired channel frequency at IF, down-converts the desired channel to DC for channel select filtering and digitalization. Since no discrete filter is present in the receive path for this topology, and the LO<sub>1</sub> is a fixed frequency synthesizer, the received signal remains wideband at the IF frequency (i.e., all the channels are present at IF). Hence, the name: wide-band IF is selected versus narrow-band at IF for the superheterodyne receiver architecture with the discrete IF filter.

With the double conversion, the image band energy is attenuated first by the RF filter and canceled by the active image reject mixers. The DC offset caused by LO leakage is eliminated with the double conversion. However, similar to the ZIF architecture, the adjacent channel energy relative to the desired channel energy is unchanged throughout the RF section of the receiver, and this limits the linearity of the baseband section [22][23]. Also, the active IR technique is subject to the I/Q gain and phase mismatches. Therefore, the sensitivity and selectivity performance of this topology strongly depend on the design complexity of the RF and baseband circuit blocks.

One key advantage of this architecture over the previous ones is that the first local oscillator is a fixed frequency synthesizer. For reasons which will be discussed in Chapter 3, this key advantage allows the PLL bandwidth to be optimized to reduce the phase noise. This enables the full integration of the frequency synthesizer, including monolithic VCOs. Although the second local oscillator is still required to be a variable frequency synthesizer tuned to the desired channel frequency, the center frequency is at a much lower frequency, inherently providing a better phase noise performance. Because it does not have discrete filters and because the frequency synthesizer is integrated, this architecture makes possible a single-chip CMOS RF receiver [26][27][28].

### **2.3 Transmitter Architecture**

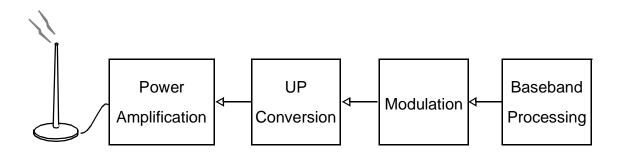

In contrast to RF receivers, RF transmitters accept baseband information (either digital or analog) and perform RF/analog signal processing to transmit the information at the carrier frequency through the antenna. Fig. 2.6 is the functional block diagram of a transmitter. The transmitter performs modulation, up-conversion and power amplification. The baseband signal is first conditioned by baseband signal pro-

Fig. 2.6: Functional Block Diagram for Wireless Transmitter.

cessing to eliminate the unwanted information in the signal spectrum. Depending on the modulation scheme for the wireless standard, the modulation and up-conversion can be combined. The up-converted signal is power-amplified for transmission through the antenna.

Sensitivity and selectivity specifications in a transmitter are more relaxed than for receivers because the input signal is generally a band-limited baseband signal; distortion and intermodulation are the important specifications. In this section, a survey of typical transmitter architectures is presented, including the *direct conversion, double conversion* and *PLL* architectures. The discussions emphasize the relative merits of each architecture, their integrability and frequency synthesizer requirements.

### 2.3.1 Direct Conversion Transmitter

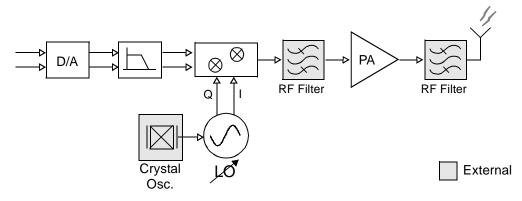

The most straightforward method to up-convert the modulated baseband information to RF is through direct conversion. Fig. 2.7 shows a block diagram of a *Direct Conversion* transmitter where the channel-select LO frequency equals the carrier frequency. The digi-

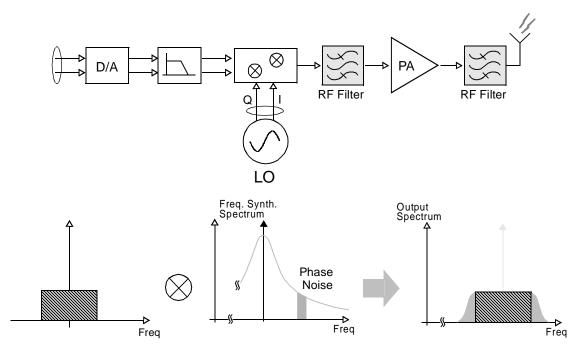

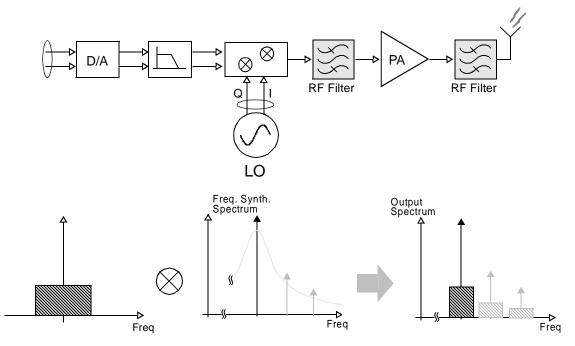

Fig. 2.7: Direct Conversion Transmitter Block Diagram.

tally modulated signal is the input to the Digital-to-Analog Converter (DAC), and the analog representation of the input signal is filtered to eliminate aliasing due to the discrete time DAC. The filtered analog waveform is up-converted directly to the carrier frequency by mixers, and it is power-amplified by the Power Amplifier (PA). External RF filters generally are required before and after the PA to eliminate noise and spurious emission in unwanted frequency bands, which limit the integrability of this architecture.

In a typical cellular telephone system, the output transmitted power can be as large as +33 *dBm*. Accounting for the insertion loss from the RF filter (worse with a duplexer), the power output from the PA may need to be 30% higher. Since the carrier frequency is identical to the LO frequency in a direct conversion transmitter, this modulated high-power PA output signal will radiate and affect the spectral purity of the nearby VCO output, which negatively impacts transmitter performance. This phenomenon is generally known as "VCO pulling" or "injection locking".

Fig. 2.8: Direct Conversion Transmitter with Offset LO.

One solution to reduce VCO-pulling problem is to use a VCO frequency different from the carrier frequency. Fig. 2.8 is a block diagram of a direct conversion transmitter using the offset LO mixing technique. The sum of the LO frequencies equals the carrier frequency; however, each LO output is not affected by the PA output because their frequencies are sufficiently far away from the carrier in the frequency spectrum. The drawback of this architecture is the generation of unwanted sideband from the offset mixing process, which may require yet an additional filter.

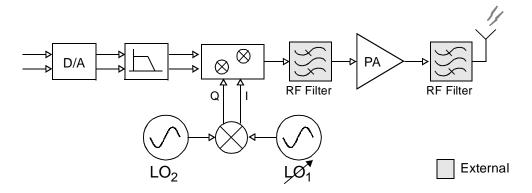

### 2.3.2 Double Conversion Transmitter

Another approach to reduce VCO-pulling is to up-convert the baseband signal in two or more steps to RF, so that the VCO frequency is far from the PA output spectrum. Fig. 2.9 is the block diagram for a *Double Conversion* transmitter. In this architecture, the baseband I/Q channels undergo the quadrature modulation at a lower frequency (LO<sub>2</sub>),

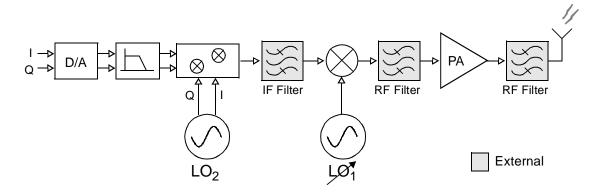

Fig. 2.9: Double Conversion Transmitter.

and the resulted IF (intermediate frequency) signal is up-converted to the transmit frequency with  $LO_1$ . The sum of the LO frequencies is the exact carrier frequency.

In addition to eliminating VCO-pulling, another advantage of double conversion over direct conversion is that the I/Q matching is better because the quadrature modulation is performed at a much lower frequency,  $LO_2$ . However, spurious tones generated by  $LO_2$  will mix with the baseband signal to the vicinity of IF, and generating an undesired image after double conversion. This is required to be attenuated to a sufficiently low level before PA with an external filter.

In order to eliminate the external filter after  $LO_1$  mixing, multiple phases of  $LO_2$  can be used to generate an approximate sine wave representation of  $LO_2$ , which can minimize the harmonic mixing for low-order harmonics [29]. Furthermore, the RF filter before PA can be removed at the expense of an additional mixer stage to perform the active image rejection. Similar to frequency synthesizer considerations in the receive path,  $LO_2$  is chosen to be variable-frequency and  $LO_1$  to be fixed-frequency to improve the phase noise

Fig. 2.10: Integrated Double Quadrature Transmitter Architecture.

performance. This architecture enables the full integration of the transmit path including the PA and is currently under investigation (Fig. 2.10) [28].

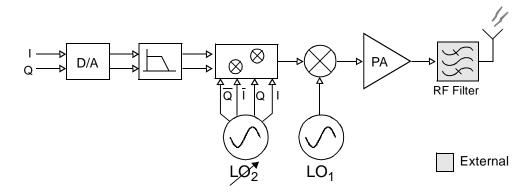

### 2.3.3 PLL-based Transmitter

One other approach to reduce the post-PA filtering requirement is to use a *PLL-based* transmitter architecture. This is shown in Fig. 2.11. In the conventional direct or two-step transmitter architectures, a RF filter or duplexer is required to suppress spurious emissions and transmit noise fallen in the receive band caused by up-conversion mixers [19]. However, a RF filter or duplexer is generally expensive and has a high insertion loss. The extra power required to overcome the RF filter insertion loss is very significant at this output power level and PA power-added efficiency (PAE). In [30], assuming a 50% PAE for a transmit output power of 2W, an extra 0.5-dB insertion loss from RF filter would require an additional current consumption of 136mA to compensate. This current consumption is large enough to power the entire transceiver.

Fig. 2.11: PLL-based Transmitter Architecture.

The PLL-based transmit architecture uses a quadrature mixer to modulate the I/Q channels to IF and a frequency translation loop, instead of a second mixer, to modulate the signal to the transmit frequency. The frequency translation loop functions as a PLL where the phase/frequency detector (PFD) detects the phase difference between the IF signal and down-converted output waveform. The error signal is fed through charge pump (CP) and loop filter (LF) to generate the VCO control voltage. This architecture minimizes the spurious tone generation (i.e., the image tone) by using a PLL, and the post-PA filtering requirement is relaxed. Therefore, it allows the use of a simple low pass filter with a small insertion loss and substantially reduces the power consumption and cost of the transmitter at the expense of the circuit complexity.

## 2.3.4 Summary

In this section, various architectures for radio receivers and transmitters have been discussed with their operations, relative merits and integrability. Considering all aspects of each architecture with complete integration as the final goal, the wide-band IF double conversion receiver (Fig. 2.5) and the double conversion transmitter (Fig. 2.10) are the most promising candidates. In addition to eliminating discrete high-Q filters in these architectures, they also allow new explorations of low-noise LO design techniques to synthesize a *fixed* RF frequency. This LO can potentially be integrated onto the same low-cost CMOS substrate with the rest of the transceiver. More details will be discussed in Chapter 3.

## 2.4 Non-idealities in Frequency Synthesizer and Their Impacts

Although there are many different types of receiver and transmitter architectures as described in earlier sections of this chapter, the frequency synthesizer function remains unchanged, namely to provide a reference frequency for the frequency translation process. In this section, a brief introduction will be given on the role of a frequency synthesizer in a receiver. Following that, the two major non-idealities of a frequency synthesizer: *phase noise* and *spurious tone*, will be presented. Their impacts on general receiver and transmitter architectures will also be discussed. More on this topic can be found in [31][32].

## 2.4.1 Role of Frequency Synthesizer

The role of a frequency synthesizer is to provide a reference frequency for the frequency translation function. Fig. 2.12 shows the RF section of a conventional superheterodyne architecture. The received RF signal is amplified by a LNA and filtered by the IR filter. The resulting signal is the input to the mixer. For simplicity, assuming the received signal,  $f_{RF}(t)$ , is a pure sine wave described by

Fig. 2.12: RF Section of Superheterodyne Receiver.

$$f_{RF}(t) = a(t) \cdot \cos(2\pi f_c t + \phi) \tag{2-1}$$

where a(t) is the amplitude variation in  $f_{RF}(t)$  and  $f_c$  is the desired signal frequency. An ideal reference frequency generated by the frequency synthesizer,  $f_{LO}(t)$ , is

$$f_{LQ}(t) = b(t) \cdot \sin(2\pi f_0 t + \Psi) \tag{2-2}$$

where b(t) is the amplitude variation in  $f_{LO}(t)$  and  $f_o$  is the LO frequency. When  $f_{RF}(t)$  is mixed with  $f_{LO}(t)$ , the resulting waveform can be described in a mathematical formula as

$$f_{IF}(t) = f_{RF}(t) \cdot f_{LO}(t) = [a(t) \cdot \cos(2\pi f_c t + \phi)] \cdot [b(t) \cdot \sin(2\pi f_o t + \psi)] \quad (2 - 3a)$$

$$= \frac{1}{2} \cdot a(t) \cdot b(t) \cdot \left[\sin\left(2\pi(f_c + f_o)t + \phi + \psi\right) - \sin\left(2\pi(f_c - f_o)t + \phi - \psi\right)\right] \quad (2 - 3b)$$

In the case of a receiver, the up-converted term  $(f_c + f_o)$  is cancelled or filtered out, and the down-converted term appears at IF where  $f_{IF} = |f_c - f_o|$ . Assuming the amplitude variation can be ignored, the resulting signal,  $f_{IF}(t)$ , is the received signal,  $f_{RF}(t)$ , mixed with an ideal reference frequency,  $f_{LO}(t)$ ; it is *frequency-translated* to an IF frequency. In

Fig. 2.13: Frequency Translation with Ideal Frequency Synthesizer Spectrum.

the case of a transmitter, the up-converted term  $(f_c + f_o)$  is preserved and the down-converted term  $(f_c - f_o)$  is filtered out to produce an up-converting frequency translation. Therefore, the role of a frequency synthesizer is to provide the reference frequency,  $f_{LO}(t)$ , for the frequency translation function.

Fig. 2.13 shows the spectral representation of the frequency translation operation for a more general case where the received signal spectrum consists of a weak desired signal and many strong adjacent channels. This case is very common in wireless communication systems today where the desired-channel user is close to the basestation while adjacent-channel users are far away. If the frequency synthesizer output is ideally a pure tone, the mixer down-converts the received signal spectrum in its entirety to an IF frequency. The respective signal strengths between desired and adjacent channels remain unchanged

Fig. 2.14: Time and Frequency Representations of Phase Noise.

until the signal passes through the discrete IF filter. In the case of superheterodyne architecture, the discrete IF filter attenuates the adjacent channel energy significantly (Fig. 2.12).

In a real world implementation, due to system noise and mismatch, the frequency synthesizer output contains *phase noise* and *spurious tones* which are the two critical performance parameters. These will be the topics of discussion in the next two sections.

#### 2.4.2 Phase Noise

In frequency synthesizer applications today, active circuits are often used to satisfy system requirements and to sustain oscillations in a lossy LC-tank oscillator. The random electronic noise associated with these active circuits causes uncertainties in the synthesizer output, and part of the uncertainties is considered *phase noise*.

Phase noise can be defined as the *random timing fluctuation in an oscillator period*. Shown in Fig. 2.14 (square wave is shown for simplicity) are the time and frequency

Fig. 2.15: Spectral Representations of Phase Noise.

domain representations of phase noise. In the time domain, the presence of random timing fluctuations in an oscillation period represents a low frequency noise modulated up to a RF frequency by the carrier frequency. In the frequency domain, phase noise is the noise energy around the center carrier. Ideally, an oscillator output spectrum centers at a single frequency. With the presence of phase noise, it spreads the carrier power over neighboring frequencies and creates the phase noise "skirt".

Phase noise is generally specified in dBc/Hz at a given offset frequency for a particular carrier. Therefore, phase noise can be found by measuring the ratio of the power spectral density (1-Hz bandwidth) at a given offset frequency to the total power at the carrier frequency. Fig. 2.15 shows a typical spectrum of a synthesizer output and a phase noise plot. The spectrum in Fig. 2.15(a) is the power spectrum of a synthesizer output with phase noise. The phase noise can also be drawn as in Fig. 2.15(b). In this log-log plot, phase noise (normalized to dBc/Hz) is plotted against the offset frequency,  $f_m$ , from the carrier,  $f_c$ . In a typical oscillator, the phase noise profile follows the curve shown, where it

traverses through  $1/f_m^3$ ,  $1/f_m^2$  and  $1/f_m^0$  slope regions. The  $1/f^2$  region is generally referred as the "white frequency" variation region, since it is caused by white or uncorrelated timing fluctuations in the period of an oscillation. The behavior in this region is dominated by the thermal noise in the devices of the oscillator circuit. The 1/f flicker noise of devices also plays an important role for low offset frequencies; therefore, the spectrum in this region falls as  $1/f^3$ . The following subsection discusses the impact of phase noise on radio transceivers.

## Receiver

A high performance superheterodyne receiver (shown in Fig. 2.12) serves as a good example to illustrate the effect of phase noise in a radio receiver. In Fig. 2.13, the frequency translation from RF to IF for a superheterodyne receiver has been shown with an ideal frequency synthesizer output. In Fig. 2.16, the ideal LO output has been replaced with a typical one having phase noise shown in the shaded areas under the curve.

In this example, the received signal spectrum consists of a weak desired channel and many strong adjacent channels. While the LO center frequency down-converts the desired channel to IF, the LO sideband phase noise energy (shown in shaded grey areas) also down-converts the adjacent channels in the received signal spectrum to IF. Since the frequency difference is the same in both cases, the down-converted adjacent channel falls in the same frequency band as the desired channel and degrades the selectivity performance of the receiver. In order to quantify the required phase noise for a typical system, an exist-

Fig. 2.16: Effect of Phase Noise in Wireless Receiver.

ing commercial wireless communication system is used as an example to calculate the phase noise requirement.

Also included in Fig. 2.16 is the blocking profile for a GSM family cellular telephone standard (DCS1800). With the reference sensitivity at -99 dBm, the nearest blocker is located at 600 kHz away from the desired channel with the maximum power of -43 dBm. Two stronger blockers, -33 dBm and -26 dBm, are located at 1.6 MHz and 3 MHz away from the desired channel respectively. The channel bandwidth for GSM is 200 kHz. To calculate the required phase noise, a few more parameters about the GSM standard must be given. System Noise Floor = -174dBm + 10log(200kHz) = -121dBm Reference Sensitivity = -99dBm System Noise Figure = 7dB (*assumed*) SNR (Signal-to-Noise Ratio) = 15dB Output Noise Floor = -114dBm

In the GSM standard, the blocker performance is measured by first increasing the desired channel energy by 3dB from reference sensitivity or, -96dBm; as a result, the effective SNR is increased to 18dB. Then a blocker signal is applied to the receiver and increased in signal strength until the output SNR drops by 3dB; or equivalently, the blocker down-converted by the phase noise increases the overall noise by a factor of 2.

Therefore, to calculate the required phase noise, the blocker down-converted by phase noise should result in the same level as the output noise floor of the system. At 600kHz, the phase noise needs to be -124dBc/Hz; for 1.6MHz and 3MHz, the phase noise is required to be -134dBc/Hz and -141dBc/Hz respectively.

## Transmitter

The function of a frequency synthesizer in a transmitter is very similar to that of a receiver shown in Fig. 2.13. It still provides a reference frequency for the frequency translation function; however, the mixer up-converts to a higher frequency.

Fig. 2.17 shows a functional block diagram of a conventional direct conversion transmitter. The digital input signal is generally a bandlimited signal that is confined within the channel bandwidth of a given system. After the D/A conversion, the LPF rejects the higher frequency aliases, and a well-conditioned baseband signal is applied to

Fig. 2.17: Phase Noise Effect for Direct Conversion Transmitter.

the mixer. With an ideal frequency synthesizer output, the baseband signal is frequency translated to the RF carrier with the direct conversion transmitter.

This frequency translation process can also be easily understood with Signals and Systems theory [33]. When two signals multiply in the time domain, it is equivalent to a convolution in the frequency domain. In an ideal case, if a bandlimited signal is convolved with a single carrier tone in the frequency spectrum, the result is a bandlimited signal at the carrier frequency. This is shown with solid lines in Fig. 2.17. When phase noise is present as in a typical LO output, the convolution will "smear" the bandlimited signal by a small amount. The resulting signal will be the bandlimited signal modulated to the carrier

frequency with spectral components beyond the band edges, shown in shaded gray color in Fig. 2.17. This creates interference to neighboring channels.

To minimize the interference to adjacent channels in the system, a *spectral mask* is generally specified by the wireless standard which regulates the maximum emission power over different frequency bands allowed by a transmitter. When the phase noise is not low enough, the signal energy spilled over to adjacent channels can exceed the emission limit after the power amplification. The transmitted spectrum then fails to satisfy the emission spectral mask in the GSM family standards or the Adjacent Channel Power Ratio (ACPR) requirement in CDMA.

## 2.4.3 Spurious Tones

The other critical performance parameter in a frequency synthesizer is the spurious tone level. Spurious tones are normally caused by phase/frequency detector and divider circuits in the feedback control path.

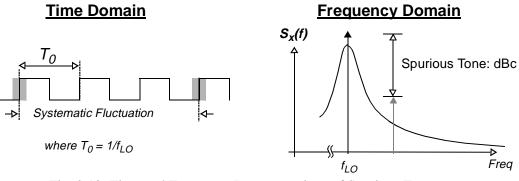

Spurious tones can be defined as *systematic timing fluctuations in an oscillator waveform*. Fig. 2.18 (a square wave is again shown for simplicity) is the time and frequency domain representations of a spurious tone. In the time domain, the presence of systematic timing fluctuations in an oscillation waveform represents a periodic timing error. In the frequency domain, it manifests as the undesired tones in the frequency spectrum. Ideally, an oscillator output spectrum centers at a single frequency with no spurious tones.

Fig. 2.18: Time and Frequency Representations of Spurious Tones.

In reality, the presence of spurious tones causes other frequency components to appear in the oscillator output spectrum.

Spurious tones are measured in dBc (or dB referenced to the carrier) at a specific frequency location in the spectrum. It is simply the power difference between the carrier and spurious tone signals in dB. In general, multiple spurious tones can be found in the output spectrum; and the location and magnitude of the spurious tones are related to the system design of the frequency synthesizer. The following subsection discusses the impact of spurious tones in radio transceivers.

## Receiver

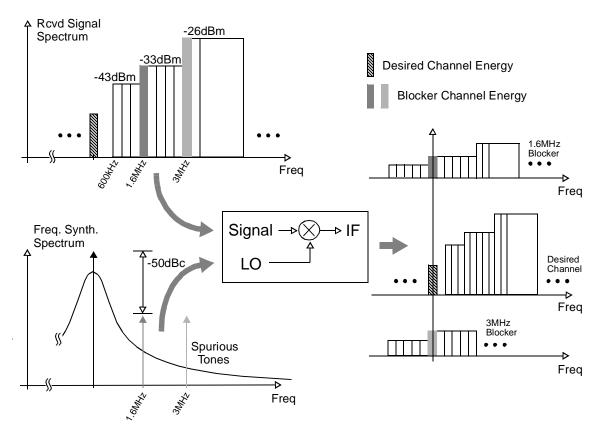

The effect of spurious tones in a radio receiver is very similar to that of phase noise. Fig. 2.19 shows a graphical illustration of the spurious tone effect on a superheterodyne receiver architecture. In the LO spectrum, two spurious tones are added at 1.6MHz and 3MHz away from the center frequency.

Fig. 2.19: Effect of Spurious Tones in Wireless Receiver.

In this example, the received signal spectrum consists of a weak desired channel and many strong adjacent channels. While the LO center frequency down-converts the desired channel to IF, the spurious tones in the LO output spectrum also down-convert the adjacent channels to the same IF frequency band (shown in shaded grey areas) and degrade the overall sensitivity of the receiver. However, since the spurious tones generally appear in predictable frequency locations, in most cases, a careful system design can be used to minimize this degradation. In the GSM family standards, six inband and twelve out-of-band spurious tones are allowed with a maximum of three adjacent channel frequencies to be assigned as spurious response exceptions. In other words, a total of eighteen spurious tones can be present in the output spectrum while no more than three are consecutive channels. When a spurious response frequency is selected, the blocking requirement is relaxed to  $-49 \ dBm$  at the frequency which the blocker is applied. For the example used in the previous section (reference sensitivity is  $-99 \ dBm$ ), the spurious tones need to be  $-50 \ dBc$  in order to satisfy the blocking specification.

## Transmitter

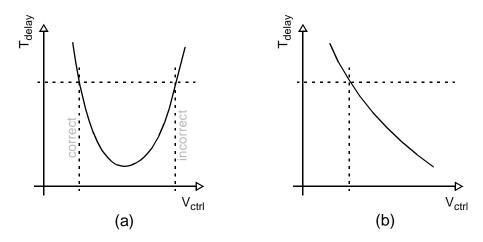

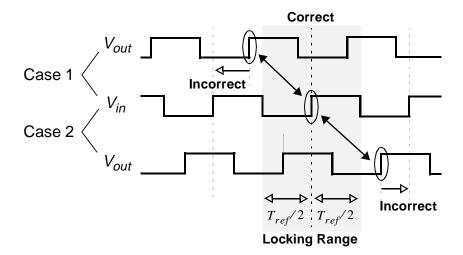

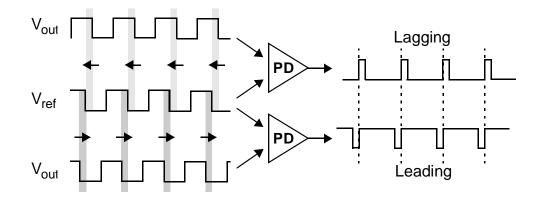

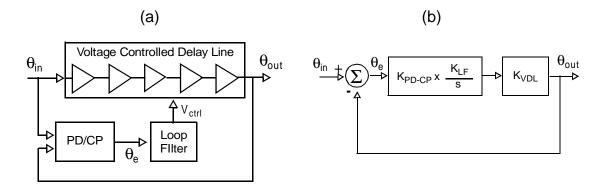

Spurious tones affect the transmitter in a very similar way as the phase noise does. While the phase noise "smears" the signal bandwidth over a wider spectrum, spurious tones mixes the desired channel to RF at the spurious tone location. Fig. 2.20 is a functional block diagram of a direct conversion transmitter with its spectrum graphs to illustrate this effect.